# 並列プログラミングとメモリコンシステンシモデル

平 田 博 章\* hrt@kit.ac.jp

## 1. はじめに

現在のコンピュータは、複数のプロセッサコ アがメモリ(主記憶装置)を共有する、共有メ モリ型の並列コンピュータとして構成される のが一般的です。いわゆるマルチコア CPU は、 高価なハイエンドのサーバーコンピュータから、 デスクトップコンピュータやポータブルコン ピュータ、さらには組み込み用コンピュータや スマートフォンに至るまで、普通に使用されて います。現在では、1個のLSIチップの中に数 十個のプロセッサコアを搭載する製品も製造・ 販売されるようになりました。しかし、複数の プロセッサコアを搭載していても、アプリケー ションプログラムが逐次プログラムとして書か れていたのでは、実行時間を短縮することはで きません。つまり、マルチコア CPU のメリッ トを得るためには、プログラマは並列プログラ ムを書かなければなりません。使用するアルゴ リズムに固有の並列性を抽出し、例えばマルチ スレッドライブラリを用いて、その並列処理単 位を1つのスレッドとして実行するよう明示的 に記述する必要があります。

共有メモリモデルに基づく並列プログラムを 作成する場合に注意すべき問題に、排他制御や 同期があります。複数のスレッドが共有する変 数に対しては、その変数にアクセスする際には ロックを掛けて他のスレッドがアクセスするこ とを禁止します。このルールを忠実に守ってプログラムを書くだけでも、実際には骨の折れる 作業ですが、一方、そのような行儀のよいプログラムを書いていたのでは実行時間が短くならない、ということもよくあります。そんな時、レベルの高いプログラスを書こうとするでし破っても速いプログラムを書こうとするで しょう。また、「ロックを掛ける」というやり 方自体に抵抗感を憶える人達もいます。Lockfree アルゴリズム(や Wait-free アルゴリズム) を開発したり使用しようとしたりする人達です。 Lock-free というのは、本来は「スレッドが止 まってしまう(ブロックされてしまう)ことが ない」という性質を意味しているのですが、実 際、やり方としてもロック機構を使用しません。

しかし、そのような試みは、容易には成功しません。俗語のレベルですが、ソフトウェアのバグの中にハイゼンバグ(Heisenbugs)と呼ばれる種類のものがあります。量子力学において不確定性原理を唱えた物理学者ハイゼンベルク(Heisenberg)の名前をもじったもので、バグの原因を突き止めようとするとバグの症状が変化したり、バグが起こらなかったりするようなバグを指します。Lock-free アルゴリズムを開発する場合や、故意にロック機構をすり抜けるようなプログラムを作成しようとすると、ハイゼンバグに遭遇していつまで経ってもデバッグが終わりそうにない、という悲惨な状況に陥ることも少なくないようです。

ただ、そのようなハイゼンバグの発生に対して「実際に何が起こっているのか?」を類推できる(あるいは、最初からそのようなバグの発生を抑制する)ためには、まず、コンピュータのハードウェアレベルで、メモリへのアクセスがどのようになされているのかを理解しておく必要があります。実際、長年ソフトウェアの開発に携わってきたベテランのプログラマでも、また、バリバリ働ける若いプログラマでも、プログラミングに活かせるハードウェアの知識を持つ人はあまりいないように感じます。そこで、本稿では、共有メモリ型並列コンピュータのメモリ機構について、プログラマからの視点を意識しながら、入門的な解説をしようと思います。

#### 2. 簡単な排他制御の例

図1のプログラムを例に考えます。スレッド A は関数 foo\_A()を、スレッド B は関数 foo\_B()を、それぞれ実行するものとします。変数 countのインクリメント(7行目、13行目)は変数 countの値を読み出して、1を加算し、その加算結果を書き戻す Read-Modify-Write (RMW)の操作で、スレッド A と B が同時に行うことは阻止しなければなりません(そうしなければ、スレッド A と B が 1 ずつ加算したのに、結果が1しか増えていない、という事態が生じるかもしれません)。従って、このRMW 操作は1つのスレッドのみが一気に(アトミックに)行わなければならず、このようなプログラム部分をクリティカルセクション(Critical Section: CS)と呼びます。

変数 a、b は、値が 1 ならば、スレッド A、Bがそれぞれ CSに入っていることを示すための変数です。スレッド A は変数 a を 1 にして、CSに入ることを宣言します(5 行目)。次に、変数 b の値を調べて、スレッド B が CS に入っていないことを確かめます(6 行目)。変数 b の値が 0 なら、スレッド B は CS には入っていないので、7 行目へと進みますが、b の値が 1 なら、0 になるまで(つまり、スレッド B が CS を出るまで)待ちます。 CS を抜けると、変数 a の値を 0 にして、スレッド A が CS にいないことをスレッド B から確認できるようにします(8 行目)。スレッド B も同様の動作です。

もしも、スレッド A が変数 a の値を1にするのと、スレッド B が変数 b の値を1にするのがほぼ同時であったならば、両者はそれぞれ6行目、13行目で無限ループに陥り、デッドロックが生じてしまいます。この点で図1のプログラムは不完全と言わざるを得ません。しかし、少なくとも、このプログラムはスレッド A と B の両方が同時に CS に入ることを阻止できるはずですが、果たしてそれは本当でしょうか?

自分がCSに入ると宣言してから、相手がCSに入っているかどうかを調べているのですから、スレッドAとBの両方がCSに入ることはなさそうに思えます。しかし、実際にはそうとは限りません。スレッドAとBの両方がCSに入ることはないと期待したとすれば、そ

```

01: int count = 0;

02: int a = 0, b = 0;

03: void foo A(void)

04: {

05:

a = 1;

while ( b == 1 );

06:

07:

count ++;

a = 0;

08:

09: }

10: void foo_B(void)

11: {

12:

b = 1;

13:

while( a == 1 );

14:

count ++;

15:

b = 0;

16: }

```

図1 排他制御のプログラム例(C言語)

れは恐らく、スレッド A が変数 a の値を1に すると、即座にスレッドBでもそれが観測で きる (読み出せる) と思い込んでいたからでは ないでしょうか。コンピュータにもよりますが、 多くの場合、スレッド A を実行しているプロ セッサコアで変数aの値を書き変えても、それ がスレッドBを実行している別のプロセッサ コアには即座には伝わりません。従って、ス レッドAが変数aの値を0から1に変更しても、 スレッドBが変数aの値を読み出すと、まだ0 としか読めないかもしれないのです。この場合、 スレッドBは14行目へと進みます。スレッド Aも、変数bの値が1になったのがまだ伝わっ ていなければ、6行目から7行目へと進み、図 1のプログラムでは排他制御できないことがわ かります。

#### 3. メモリコンシステンシモデル

メモリコンシステンシモデル(Memory Consistency Model)[1-3] は共有メモリへのアクセス順序とプログラム実行の正当性との関係を扱うモデルです。イベントオーダリングモデル(Event Ordering Model)と呼ぶ場合も

あります。

メモリ(主記憶装置)の速度はプロセッサに 比べるとかなり遅いのが現実です。メモリに1 回アクセスするだけの時間で、プロセッサでは 整数の足し算を 100 回以上行うことができるほ どの差があります。また、メモリの同じ番地に 複数のプロセッサから同時にアクセスすること はできません。メモリ装置としての性質がそう いうものですからどうしようもありません。そ こで、プロセッサコア (ごと) にキャッシュメ モリを配置して、プロセッサから見たメモリの 性能を見かけ上、向上させています。キャッ シュメモリは主記憶装置ほどの容量はありませ んが、その代わり速度の速いメモリ素子を用い て構成します。頻繁に使用する命令語やデータ のコピーを一時的にキャッシュメモリに格納し、 プロセッサコアからは、通常、メモリではなく キャッシュメモリにアクセスすることで、メモ リアクセス性能を向上します。

キャッシュメモリをどのように制御するか、 また、キャッシュメモリとメモリとをどのよう なネットワークで接続するか、によって、他の プロセッサコアが変更したデータをいつ読める ようになるのか、あるいはどんな順序で読める のか、も影響を受けます。プログラムの側から 見れば、書き込んだ順に他のプロセッサコアで 読めるのが最も望ましいのですが、決められた ある順序を守るように制約を課すことは、概し て高速化を妨げることになります。同時に処理 することで高速化するのですから、順序化はそ れとは逆の行為です。一方、順序制約を緩和し すぎて、やりたいことがプログラムとして表現 できないということになれば、それはそれでコ ンピュータとして使い物になりません。そこで、 高速化と正しいプログラムが書けることとの間 での調整が必要になります。それを規定したも のがメモリコンシステンシモデルです。

並列コンピュータのメモリアーキテクチャの発展の過程で、いくつかのメモリコンシステンシモデルが提唱されてきました。モデルとしては、ハードウェアの詳細は隠蔽して、結果的にどのような順序制約が緩和されたり追加されたりしているかのみを提示しています。ハードウェアの理解がなくてもそのモデルで定義され

たルールに従えば良いのですが、逆に、その ルールの根拠が示されないので、理解しづらい ものとなってしまっているとも言えます。以降、 代表的なメモリコンシステンシモデルについて 説明します。

## 4. Total Store Ordering

Intel 社の x-86 アーキテクチャで採用されているモデルが Total Store Ordering (TSO) [4]です。古くからある命令セットアーキテクチャを基に並列コンピュータを構成する際に開発したもので、並列コンピュータとしては比較的速い時期に開発されたためか、ライトスルー方式のキャッシュアーキテクチャを色濃く反映したモデルとなっています。

あるプロセッサコアが書き込んだ値を他のプロセッサコアが読み出せるようになるまでに遅れが生じることを許していますが、最大の特徴は、モデル名が示す通り、あるプロセッサコアが行なった書き込みの順序は、そのままの順序で他のプロセッサコアに観測される点です。例えば、プロセッサコア A で変数 x に3を書き込んだとします。さらにその後、別のプロセッサコア Bが変数 x を読み出す場合、3を書き込む前の値が読める(3 はまだ読めない)かもしれません。一方、変数 y を読み出して 4 が読めたのなら、その前に書き込まれた x の値は 3 が読めることが保証されます。

ライトスルー方式では、プロセッサコアがメモリに書き込む場合、実際にはキャッシュメモリとメモリの両方に書き込みます。しかし、書き込みを行うたびにメモリにアクセスしていたのでは高速化できません。そこで、一般的には、ライトバッファをキャッシュメモリに併設して、メモリに直接書き込む代わりに、ライトバッファに書き込みます。ライトバッファに書き込まれた値は、後で、書き込まれた順にメモリに書き込みます。従って、他のプロセッサコアからは、書き込まれた順番にその結果が読み出せるのです。TSOは、このようなライトバッファの存在に対応して考案されたモデルと言えます。

性能の点では、ライトスルー方式よりもコピーバック方式のキャッシュメモリの方が一般

的に優れているのですが、1台のプロセッサコ アで行なった書き込みの順序が保存されるため、 プログラムはまだ書き易いと言えます。

#### 5. Partial Store Ordering

コピーバック方式(つまりはライトスルー方 式ではない)のキャッシュメモリの場合や、ス トアユニットを複数持つスーパスカラプロセッ サの場合に自然に対応するモデルが Partial Store Ordering (PSO) です。コピーバック方 式では、ライトバッファを用いません(ライト バッファが不要です)。ライトバッファがある ことで、書き込みの順序をプログラムの通りに 保存できたのですが、それがないため、書き込 みの順序は保存できません。また、ストアユ ニットを複数設けるのは、キャッシュメモリに 同時に複数のデータを書き込むのが目的です。 しかし、この場合は、キャッシュメモリに書き 込む時点で、すでに、プログラムの順序とは異 なっていると考えられます。PSO は、このよ うな特質を反映して考案されました。

TSOでは、1台のプロセッサコアで行なったすべての書き込みに対してその順序が保存されますが、PSOでは、同じアドレスに対して行った書き込みの順序のみが保存されます。異なるアドレスに対して行った書き込みは、プログラムの順序とは異なって観測される、という点に注意する必要があります。

再び、図1のプログラム例で考えてみましょ う。今回はスレッドAとBがクリティカルセ クションに入る際に競合せず、スレッド Aが 先に関数 foo A() の実行を終了したとします。 関数 foo\_A() の中で、スレッド A は、まず、 変数 a に 1 を書き込み、次に変数 count に 1 を 書き込み、最後にaに0を書き込みます。その 後、スレッドBがfoo\_B()を実行します。こ の時点で変数 a の値が 0 であることが観測でき ると、クリティカルセクションに入って count をインクリメントします。その結果、count の 値が2になることを期待するのが普通でしょ う。実際、TSOであったなら、期待通りの結 果が得られます。しかし、PSO ではそうとは 限りません。最終的な count の値は、2 かもし れませんが、1かもしれないのです。変数 a と

count は異なる変数ですので、スレッド A での書き込みの順序はスレッド B からは異なって観測される可能性があります。つまり、8 行目の結果として 13 行目で変数 a の値が 0 と読めたからといって、14 行目で count の値を読み出すときに 7 行目の結果が読み出せるとは限りません。

しかし、これでは期待した通りのプログラム を書くことはできません。そこで、メモリアク セスの順序に制限を加える命令が用意され、必 要なときのみその命令を用いてメモリアクセス の順序を制御できるようになっています。図1 のプログラムでは、7行目と8行目の間、また 14 行目と 15 行目の間に、メモリバリア(また はメモリフェンス)と呼ぶ操作を行う命令を挿 入する必要があります。これにより、メモリバ リアの前に記述されたメモリアクセスが完了し てから、メモリバリアの後に記述されたメモリ アクセスを開始します。このようにメモリバリ アを挿入することにより、スレッドAが変数 countに1を書き込んだ後に、変数aに0を書 き込んだことが(他のプロセッサコア上で実行 されている) スレッド B からも観測できるよ うになります。つまり、変数aの値としてOが 読めたなら、変数 count の値は必ず 1 が読める ようにできます。

メモリアクセスの順序に関する制約が緩和されるほど、高速にプログラムを実行できる可能性が高まります。しかし、その一方で、そのようなハードウェアの特質を最大限に活かすためには、プログラムを作成する際に上記のような注意が必要になります。メモリバリアに関する命令やメモリバリア機能の種類は、プロセッサの種類(アーキテクチャ)によって異なりますので、アセンブリ言語との組み合わせでプログラムを記述する必要があります。しかし、例えばgccの場合は、組み込み関数\_sync\_synchronize()を呼び出すことで、一般的なメモリバリア操作を実行することができます。

## 6. Weak Consistency

PSOではメモリバリアなどの同期命令が必要になりますが、それも含めてメモリコンシステンシモデルとして定義した方がスッキリしま

す。ということで、メモリへのアクセスは読み 出し/書き込みだけでなく、同期も含めてその 順序制約を考えます。そのようにして考案され たのが Weak Consistency (WC) です。WC は、 IBM 社の POWER/PowerPC で採用されてい ます。

WCでの同期命令には、メモリバリア操作を行う命令のほか、同期機能を伴うメモリの読み出しや書き込みを行う命令(さらには演算を行うものもあります)も含めて考えます。実際にどのような命令が用意されているかはプロセッサのアーキテクチャによって異なります。基本的には、クリティカルセクションの入口と出口で同期命令を実行するものとして考えます。

WCのルールは次のようなものです。まず、 (i) プログラム上で同期命令よりも前に記述さ れた読み出しや書き込みは、その同期命令を実 行する前に完了しなければなりません。また、 (ii) 同期命令よりも後に記述された読み出しや 書き込みは、その同期命令が完了してから開始 しなければなりません。そして、(iii) 同期命 令同士は、プログラムに記述された順序で実行 (完了)しなければなりません。異なるプロセッ サコアで実行される同期命令の順序はどれが先 でも構いませんが、全てのプロセッサコアにお いて同じ順序で観測される必要があります。あ る同期命令から次の同期命令までの間に行われ る読み出しや書き込みの順序には一切の制約が ありませんので、それらの実行(や完了/観測) の順序が入れ替わっても問題ありません。

プロセッサコアのハードウェア機構とWCとの関係は、PSOの場合とあまり変わりはありません。図1のプログラムを例にしたメモリバリアの話は、WCでもそのまま当てはまります。これはクリティカルセクションの出口での処理についての話であり、上記のルール(i)に関連します。

さて、メモリアクセスの順序が入れ替わる原因は、キャッシュメモリの制御方式だけではありません。例えば、高速化のためのデータの先読み(プリフェッチ)や、スーパスカラでの命令の動的スケジューリングによって命令の実行順序が入れ替わる場合、があります。再び、図1のプログラムを用いてその様子を見てみま

しょう。スレッド A が先にクリティカルセク ションに入り、変数 count の値を 1 にしてメモ リバリア命令を実行した後に、変数 a の値を 0 にします。その少し後にスレッドBがクリティ カルセクションに入る場合を考えます。スレッ ドBは変数aの値が0であることを確認して からクリティカルセクションに入るので、14 行目で変数 count を読み出すと1が読めるはず です。ところが、データの先読みを行なってい ると、変数 a の値を読むよりも先に count の 値を読み出しているかもしれません。その場 合、スレッド A が 1 を書き込む以前の値を読 んでしまっていることになります。従って、こ こでもメモリバリアが必要になります。つまり、 6行目と7行目の間、また13行目と14行目の 間に、メモリバリア命令を挿入して、データの 先読みを抑止する必要があります。これは先の ルール(ii)に関連します。

これまで見てきたように、プロセッサの高速 化を実現するアイデアを実装すると、メモリア クセスの順序がプログラムで記述された順序と 異なってしまうことが起こり得ます。言い換え れば、プログラムで記述されたメモリアクセス の順序をそのまま守るのではなく、順序制約を 緩和することでプロセッサを高速化していると 言えます。どのような順序制約が残されている かを、ハードウェア機構の詳細を隠してモデル 化したものがメモリコンシステンシモデルです。 高速な並列プログラムを書こうとするなら、

メモリコンシステンシモデルの理解は必須です。

#### 7. 実例 - 二分探索木の並列生成

一般に、クリティカルセクションに入る前にはロックをかけ、クリティカルセクションを出るときにロックを解放することで、排他制御を行います。きちんとロックをかけるプログラムを書く場合には、メモリコンシステンシモデルを意識する必要はありません。とは言っても、もちろん、メモリバリア命令などが不要なわけではありません。ロック関数やアンロック関数の中で必要な同期命令を実行するように書かれているために、それらの関数を使用してアプリケーションプログラムを作成する場合には、同期命令を意識する必要がないだけです。逆に、

No. 42 2023 - 19 -

ロック / アンロック関数を作成するシステムプログラマには、メモリコンシステンシモデルの正確な理解が要求されます。

さて、ここでは、二分探索木を並列に生成するプログラムを考えてみます。ただし、プログラム実装の詳細にはあまりふれずに、実行時間における効果を示すだけにとどめます。

まず、図 2 に二分探索木のノードの定義 (Node) と、そのノード内のリンクの初期化関数 init\_node\_link()を示します。ここでは、ノードのキーは int 型で定義しています(8 行目)。各ノードには、左右の子ノードを指すリンク (Link) が必要です(10 行目)。1 つのリンクは、子ノードを指すポインタとロック変数を対にして定義します( $3\sim6$  行目)。

変数 tree は二分探索木の根ノードを指すリンクです(12 行目)。ポインタは NULL、ロック変数はアンロックされている状態を示す値(ここでは LockInitVal とします)で、それぞ

れ初期化します。また、関数 init\_node\_link()は、引数に与えられたノードの左右のリンクを初期化する関数です。

二分探索木の並列生成アルゴリズムは、逐次アルゴリズムから簡単に導出できます。図3は、きちんとロックをかけて二分探索木を生成するプログラムを示しています。各スレッドは関数 insert()を実行して、その引数ndが指す新しいノードを二分探索木に挿入します。関数insert()では、根ノードから葉ノードに向かって、ノードの挿入場所を探しながら二分探索木中のノードを順にたどります。変数 cur が、現在立ち寄っている二分探索木中のノードを指すリンクです。そのノードを直接指すポインタとして、変数 t を用いています。

複数のスレッドが同時に同じ場所にノードを 追加しようとするかもしれませんので、そのポインタへの書き込みには排他制御が必要になり ます。また、あるスレッドが読み出そうとする ポインタに、別のスレッドが書き込もう(ノー

```

01: typedef struct node Node;

02: typedef struct link Link;

03: struct link {

Node *ptr;

04:

Lock t lock;

05:

07: struct node {

08:

int key;

09:

10:

Link left, right;

11: };

12: Link tree

= { NULL, LockInitVal };

13: void init node link(Node *nd)

14: {

15:

nd->left.ptr = NULL;

16:

nd->left.lock = LockInitVal;

17:

nd->right.ptr = NULL;

18: nd->right.lock = LockInitVal;

19: }

```

図 2 ノード定義と初期化関数 (C 言語)

```

01: void insert(Node *nd)

02: {

03: Link *cur = &tree;

04:

Node *t;

05:

while(1) {

06:

Lock(&(cur->lock));

07:

if( (t=cur->ptr) == NULL ) {

08:

init_node_link(nd);

09.

cur->ptr = nd;

10:

Unlock(&(cur->lock));

11:

return;

} else {

12:

Unlock(&(cur->lock));

13:

14:

15:

if(nd->key < t->key)

16:

cur = &(t->left);

17:

else

18:

cur = &(t->right);

19:

20: }

```

図3 並列ノード挿入プログラム(C言語)

ドを追加しよう)としているかもしれませんから、書き込み同士だけではなく、読み出しと書き込みの間でも排他制御が必要です。従って、リンクを辿るときにはまずロックを掛けて(6行目)、ポインタを読み出します(7行目)。それが NULL であれば、そこが挿入場所ですから、新たに挿入するノードのリンク欄を初期化して(8行目)、ノードを追加します(9行目)。これで挿入を完了しましたから、ロックを解放して(10行目)、関数 insert()での処理を終了します(11行目)。

まずは正しい並列プログラムを書く、という 観点では、図3のプログラムで良しとするべき でしょう。しかし、後で述べますが、このプロ グラムでは期待するほど高速に二分探索木を生 成できません。むしろその結果にがっかりして しまって、これが最初の並列プログラミング体 験だったとしたら、並列処理などやる価値がな いと思ってしまうかもしれません。

これを高速化したプログラムは、図3の6~14行目を図4の2~13行目で置き換えることによって得られます。ノードの追加は、値がNULLのポインタを、追加するノードへのポインタ値で置き換えることによって行います。NULLでないポインタを書き換えることは行い

```

01: #define MR(A) ¥¥

(*((Node * volatile *)(A)))

02: if((t = cur->ptr) == NULL)

03:

Lock(&(cur->lock));

04:

if( (t = MR(cur->ptr))

== NULL ) {

05:

init_node_link(nd);

__sync_synchronize();

06:

07:

cur->ptr = nd;

08:

Unlock(&(cur->lock));

09:

return;

} else {

Unlock(&(cur->lock));

11:

12:

}

13: }

```

図4 高速なノード挿入プログラム (C 言語)

ません。アルゴリズム上のこのような特徴を利用して、まずはロックを掛けずに、いま立ち寄るノードへのポインタ(cur->ptr)を読み出し(2行目)、それがNULLでなければそのノードをたどります(図3の15行目に進みます)。一方、NULLであった場合には、そこが挿入場所である可能性がありますので、この時点でロックを掛け(3行目)、そののちに再度、cur->ptrの値を読み直します(4行目)。

4行目ではマクロ MR() を用いて読み直し ていますが、その定義は、1行目に示すように、 一見しただけでは非常に理解しづらい型にキャ ストする(だけの)ものです。cur->ptrの値 は2行目で既に読み出していますので、コン パイラが、4 行目ではメモリから読み出さずに 2行目で読み出した値を使うようにする可能性 があります。しかし、2行目では cur->ptr は NULLであったものの、4行目に進むまでの間 に他のスレッドが書き換えているかもしれませ んから、4行目でも NULL であるとは限りませ ん。そこで、コンパイラの最適化機能を制止し て、再度、cur->ptrの値をメモリから(実際 にはキャッシュメモリからかもしれませんが) 読み出すようにするために、volatile 修飾子を つけてキャストしています。

ところで、ロックを掛けて実行しなければならないクリティカルセクションの中でアクセスするデータに、ロックを掛けずにアクセスすることを許すのは、本来はやってはいけないことです。しかし、そのやってはいけないことを図4のプログラムではやるのですから、それによってどのような不具合が生じ得るかをすべて把握し、対策できていなければなりません。

例えば、図4では、6行目でメモリバリア操作を行っています。TSOを用いている x86系のコンピュータでこのプログラムを実行する場合には、ここでのメモリバリアは不要(冗長)です。しかし、メモリコンシステンシモデルにPSOやWCを採用しているコンピュータで実行する場合は必須となります。

PSO や WC のコンピュータで、6 行目が欠落したプログラムを実行した場合にどのようなことが起こり得るかを考えてみましょう。スレッド A が、ノード X を二分探索木中のノー

ドYの子ノードとして追加するとします。ス レッドAはノードX内のリンクを初期化して (5 行目) から、ノード Y にノード X を追加 (7 行目)します。別のスレッドBはロックを掛 けずに、ノードYからノードXへとたどって くるかもしれません。そしてさらに、ノード Xの子ノードへと進むでしょう。プログラム 上ではノードX内のリンクを初期化した後に ノード Y からノード X ヘリンクを貼っていま すが、スレッドBからは、ノードYからノー ドXへとたどった後でも、ノードX内のリン クは、初期化する前の値がまだ見えているかも しれません。その結果、スレッドBは誤った 場所をたどろうとするか、あるいはセグメント 違反を起こして異常終了してしまうことになり ます。このようなことを防ぐために、クリティ カルセクションの中であるにもかかわらず、メ モリバリア操作を6行目で行う必要があります。

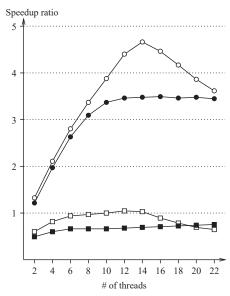

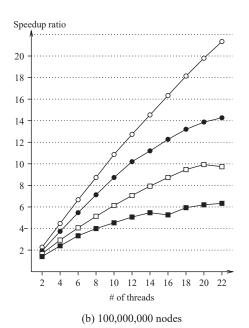

最後に、図3のプログラムと図4のプログラ ムで、性能がどのように異なるかを見てみます。 12 コア 24 スレッドのインテル Xeon プロセッ サで実行した結果[5]を図5に示します。横 軸がスレッド数を、縦軸が1スレッドで実行 した場合に比べて何倍速いかを示しています。 M3 と S3 が図 3 のプログラム、M4 と S4 が図 4のプログラムの結果です。M3と M4ではロッ クにサスペンドロック (Mutex) を、S3 と S4 ではスピンロックを用いました。測定条件など の詳細は省きますが、ノード数が1万個の二分 探索木を生成する場合(図5(a))には、図3 のプログラムでは速くなるどころか、逆に1ス レッドで実行するよりも遅くなっています。1 億ノードの場合(図5(b))はスレッド数を増 やすと性能は向上しますが、それでも図4のプ ログラムと比べると半分以下の性能です。

#### 8. おわりに

メモリコンシステンシモデルについて、並列 プログラミングの観点から解説しました。実は、 本稿では紹介しませんでしたが、WCの順序 制約をさらに緩和したモデルとして、Release Consistency (RC) [6] が考案されており、例 えば ARM (v8) や RISC-V など、比較的最近 に開発されたプロセッサアーキテクチャは RC

(a) 10,000 nodes

図 5 性能比較

を採用しています。

期待通りに安定して動かすためには、あまりアグレッシブな並列プログラムは書かない方がよいのですが、それでは並列コンピュータの性能を十分に引き出すことはできません。一方、プログラム実行時に生じる種々の動作タイミングの組み合わせで何が起こり得るかを正確に把握して、それをプログラム中で対処・制御するのは容易ではありません。私もハイゼンバグに

悩まされることもあれば、バグの原因の見当をつけようと真剣に考える過程で、あまりにもややこしくて脳ミソがとろけそうな感覚を覚えることもありますが、それでも絶望的な状況に陥らないのは、やはり、ハードウェアの動作やメモリコンシステンシモデルの理解が助けになっているのだろうと感じています。

# 参考文献

- [1] H. Hennessy, and D. A. Patterson. "Computer Architecture – A Quantitative Approach (6<sup>th</sup> Edition)." Section 5.6, Morgan Kaufmann Publishers (2019).

- [2] 天野英晴著「並列コンピュータ」第3章, 昭晃堂 (1996).

- [3] D. J. Sorin, M. D. Hill, and D. A. Wood. "A Primer on Memory Consistency and Cache Coherence." Morgan & Claypool Publishers (2012).

- [4] P. Sewell, S. Sarkar, S. Owens, F. Z.

- Nardelli, and M. O. Myreen. "x86-TSO: A Rigorous and Usable Programmer's Model for x86 Multiprocessors." Communications of the ACM, vol. 53, no. 7, pp. 89–97 (2010).

- [5] H. Hirata, and A. Nunome. "Parallel Binary Search Tree Construction Inspired by Thread-Level Speculation." Proceedings of the 23rd International Conference on Software Engineering, Artificial Intelligence, Networking and Parallel/Distributed Computing, pp. 74–81 (2022).

- [6] K. Gharachorloo, D. Lenoski, J. Laudon, P. Gibbons, A. Gupta, and J. Hennessy. "Memory Consistency and Event Ordering in Scalable Shared-Memory Multiprocessors." Proceedings of the 17th Annual International Symposium on Computer Architecture, pp. 15-26 (1990).

No. 42 2023 - 23 -